KEIm-CVSoC 製品紹介

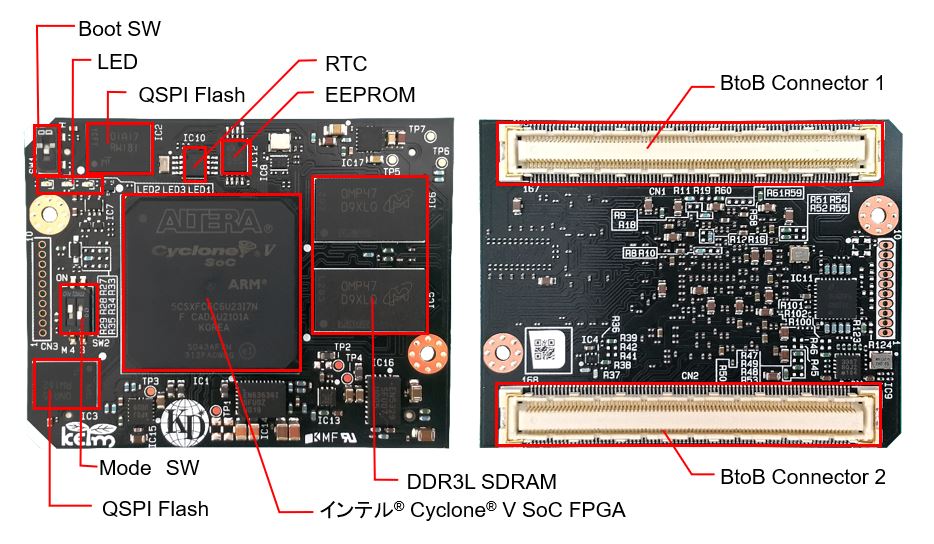

製品外観

レイアウト

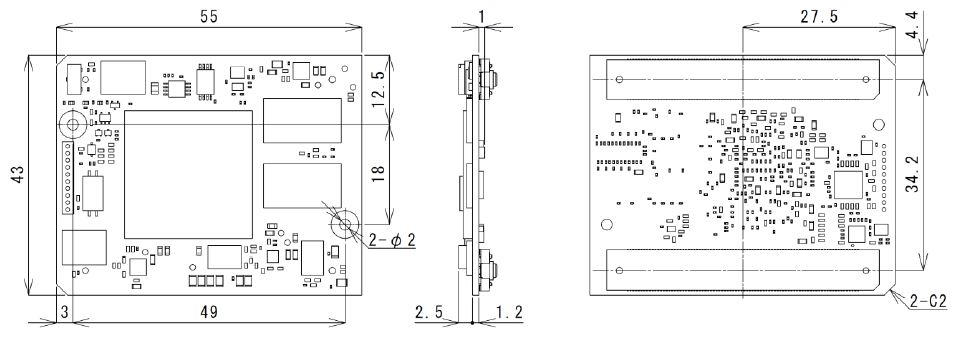

外形図

仕様一覧

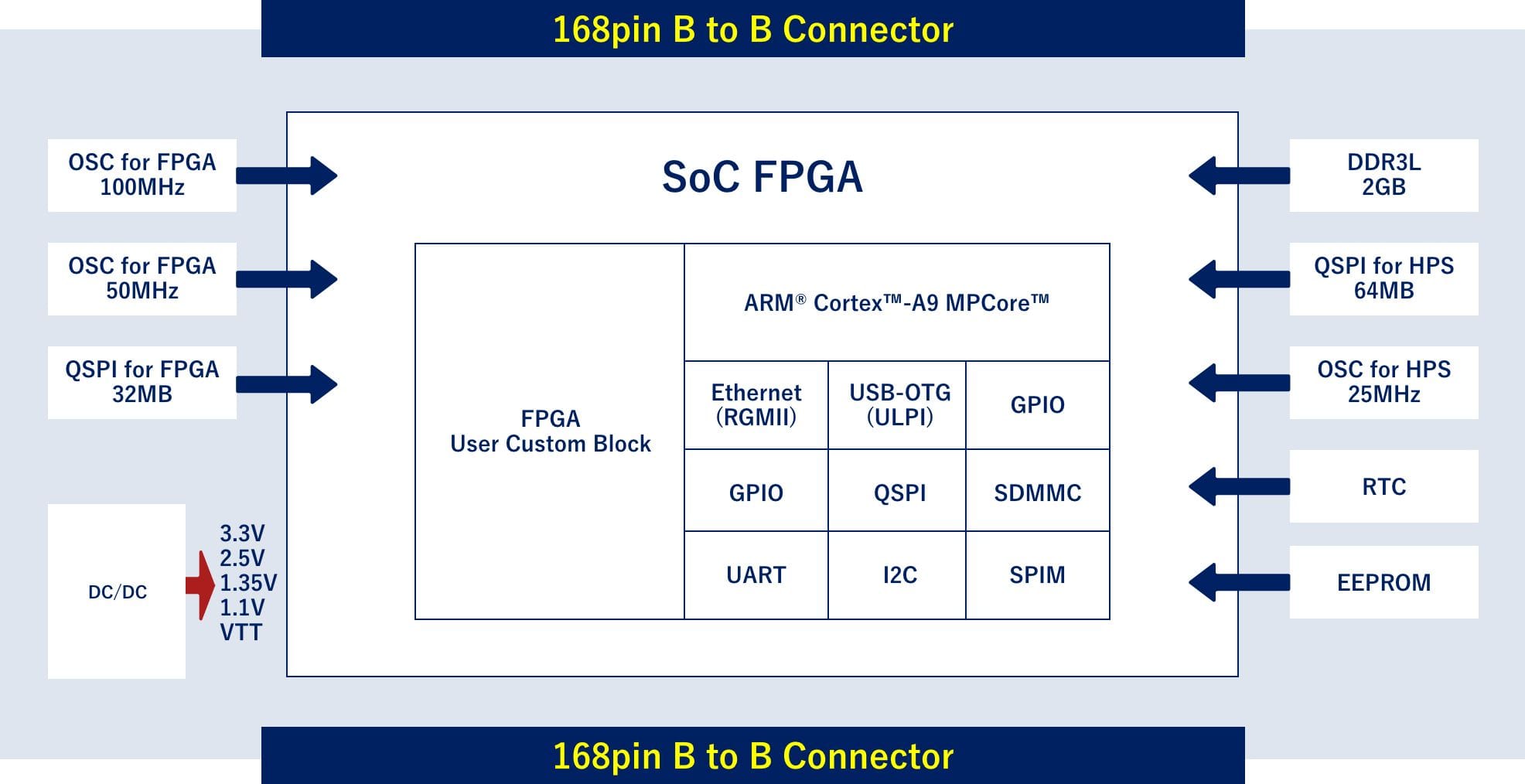

SoC FPGA

| Cyclone® V SoC FPGA | |

| デバイス型式 | 5CSXFC6CU23I7N |

| Hard Processor System | ARM® Cortex™ -A9 MPCore™ HPS |

| Logic Elements / ALMs | 110kLEs /41,910ALMs |

| M10K memory | 5,570kbits / 557blocks |

| MLAB memory | 621kbits |

| DSP blocks | 112 |

| 18 × 18 multipliers | 224 |

| PLLs(HPS) | 3 |

| PLLs(FPGA) | 6 |

| Transceiver count(3.125Gbps) | 6 |

メモリ

| DDR3L SDRAM(HPS) | 2GByte, バス幅 32bit MT41K512M16VRN-107 IT (Micron)×2 |

| QSPI Flash(HPS) | 64MByte MT25QL512ABB8E 12-0SIT(Micron) |

| QSPI Flash(FPGA) | 32MByte, コンフィグレーション用 MT25QL256ABA8E12-1SIT (Micron) |

クロック

| HPS用 | 25MHz |

| FPGA用 | 50MHz, 100MHz |

ペリフェラル

| RTC | DS1339U-33+(Maxim), バッテリは外付け |

| EEPROM | 24LC32A-I/ST(Microchip), 32bit |

| LED | x3 |

コネクタ

| 168ピン基盤間コネクタ × 2 | |

| コネクタ形式 | FX10A-168S-SV(HRS) |

| HPS IO | Ethernet(RGMII)×1, USB OTG(ULPI)×1, SPIM×1, UART×1, I2C×1, QSPI×1, SDMMC×1, GPIO×21 |

| FPGA IO | 最大133本 |

| Transceiver | T×6レーン, R×6レーン |

| JTAG I/F | HPS-FPGA デイジーチェイン 別売りのインテル® FPGA ダウンロード・ケーブル Ⅱを使用してデバッグが可能 |

| 入力電源 | +3.3V±5%(3.135〜3.465V),VCCIO(3.3V or 2.5V) |

| 消費電流 | TBD |

| 使用温度範囲 | -40℃~85℃ |

| 外形寸法 | 55×43mm |

デザイン例

※FPGA又はSoC FPGA内の構成はデザインにより異なります。図は標準的な構成例です。

開発環境

KEIm-CVSoC 開発キット

| SoM | KEIm-CVSoC |

| カメラ入力 | OV5647カメラモジュール (1080p30, MIPI CSI-2) |

| 映像出力 | DVI出力, ミニHDMIコネクタ x1 (DVI出力) |

| Ethernet | RJ45コネクタ x1 (10/100/1000Base-T) |

| USB 2.0 OTG | USBマイクロABコネクタ x1 (High Speed) |

| UART | USBマイクロBコネクタ x1 (USB シリアル) |

| M.2スロット | 別売りのIEI Mustang-M2BM-MX2を接続可能 |

| LED | x4 |

| デバッグI/F | 別売りのインテル®FPGAダウンロード・ケーブルIIを接続可能 |

| 入力電源 | 12±5%, 付属ACアダプタより供給 |

| 付属品 | ACアダプタ USBマイクロType-Bケーブル |

技術サポート

以下の資料をダウンロードできます。

- KEIm-CVSoC ハードウェアマニュアル

- KEIm-CVSoC 開発キットスタートアップマニュアル

- KEIm-CVSoC 各種リファレンスデザイン